- Backward compatible with Systran CPCISC2

- Slave dual industry pack carrier, CPCI 3U format

- 5 volts PCI signaling

- Support for up to two IP modules

- 8 MHz IP operation Per slot

- Direct I/O or Memory mapped access from CPCI bus via PCI Chip

- Supports double-wide form factor Industry Pack

- Full interrupt support of host

- Front panel I/O connectors for all IP’s

- Up to 100 I/O’s on one single slot

CPCISC2

CPCI Slave Dual Industry Pack Carrier 3U

- Backward compatible with Systran CPCISC2

- Slave dual industry pack carrier, CPCI 3U format

- 5 volts PCI signaling

- Support for up to two IP modules

- 8 MHz IP operation Per slot

- Direct I/O or Memory mapped access from CPCI bus via PCI Chip

- Supports double-wide form factor Industry Pack

- Full interrupt support of host

- Front panel I/O connectors for all IP’s

- Up to 100 I/O’s on one single slot

Share this product

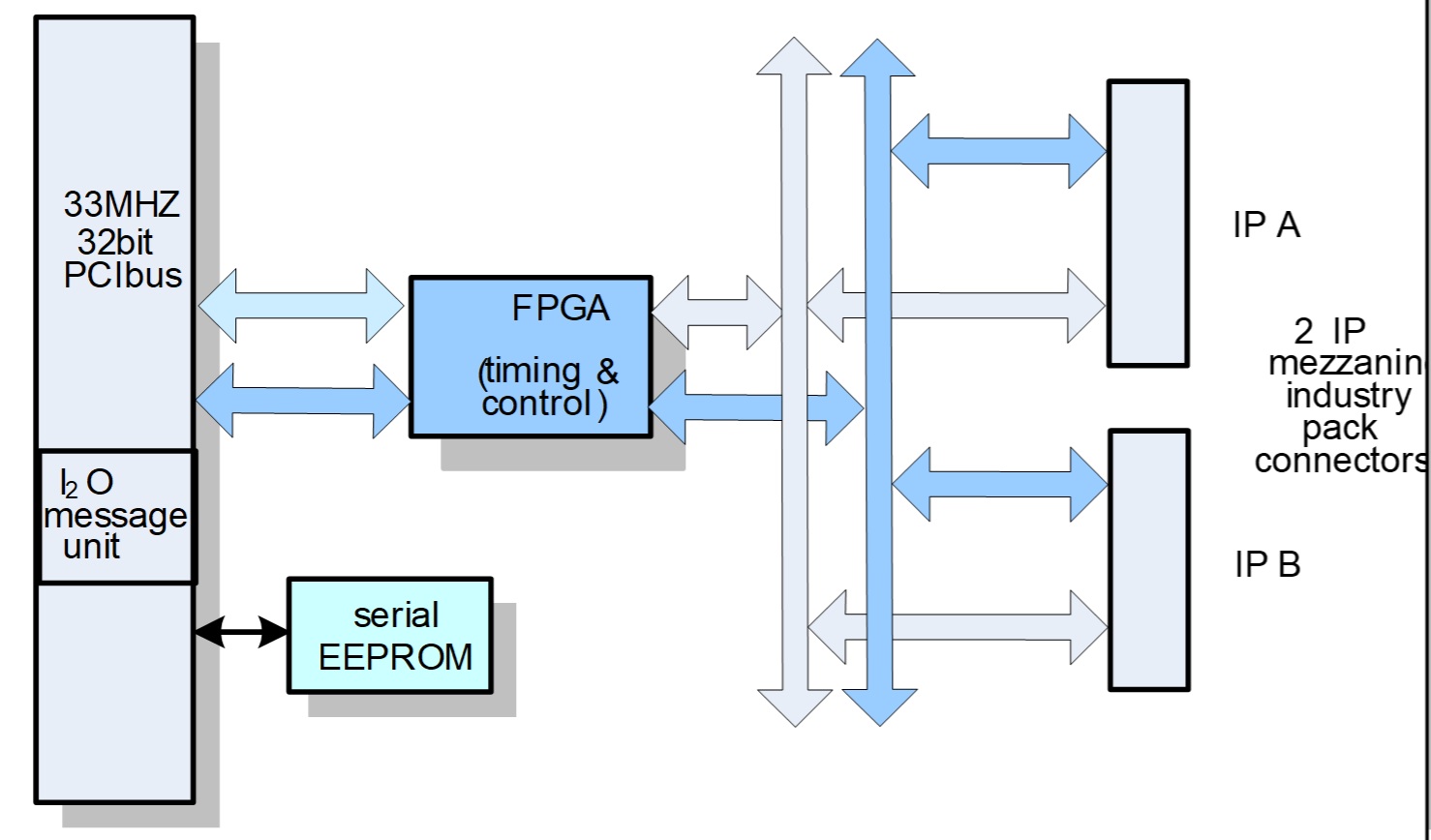

The CPCISC2 is a 3U format slave Compact PCI (CPCI) bus IP carrier. The CPCISC2 provides mechanical support and the electrical interfaces for two single width IP modules, or one double width IP modules. Multiple CPCISC2 boards may be installed in a single system.

Available Software Drivers:

- Labview

- Linux

- Window XP

Applications:

- For application requiring low cost, high density I/O or unique I/O combinations, the CPCISC2 is the perfect solution.

Industry Pack Specifications:

- Meets ANSI/VITA 4-1995

- 8 MHz synchronous operation

- Supports ID, 128 byte I/O, interrupt. & 8 Mbyte memory spaces

- 2 Interrupts per module

- Two passive DMA channels are possible.

- Hardware self timed per IP module

- Triggered via system reset and software control

- Jumper or software time-out function

- 5, +/-12 volt reset-able fuse per IP

- 8/16 bit data on 3U board, 32 bit on 6U board

Operating Environment:

- Operating temperature Commercial: 0 to +70 ºC Optional: -40 ºC to +85 ºC

- Non-operating: -55 ºC to +100 ºC

- Airflow requirement – 5 CFM

- Humidity – 5 to 90% (non-cond)

- Altitude – 0 to 10,000 feet

Mechanical Environment:

- Size – 3U CPCI module 100mm x 160mm

- Power – 1 watt

- Vibration – 0.5G, 20-2000 Hz rand

- Shock – 20G, 11 msec, ½ sine

- Weight – 5 ounces

- MTBF – >250,000 hours

PCI Bus Controller Features:

- PCI Bus:

- 32-bit, PCI r2.2 compliant

- Motorola PowerQUICC and generic 32-bit, 33MHz local bus modes

- 5V tolerant bus interfaces

- PICMG 2.1 r2.0

- Zero wait state burst operation, with PCI bus bursts to 264 MB/sec and local bus bursts to 264 MB/sec

- 2 DMA channels

- Direct master data transfers

- Direct slave data transfers

PCI Bus Control:

- I2O r1.5 messaging unit

- 8 mailboxes and 32 doorbell registers

- PCI arbiter supports 7 external masters

- Host mode reset/interrupt

- Power management event generation support

- Serial EEPROM interface

Ordering Information:

- CPCISC2-ATC 3U CPCI

Slave Industry Pack Carrier with Front I/O only - CPCISC2-ATC-I

Same as above but Industrial temp: -40 ºC to +85 ºC

Optional Accessories:

- CBL-50-HDR Cable

- TB-50-HDR Terminal block

Data Sheet – Link Here

- Backward compatible with Systran CPCISC2

- Slave dual industry pack carrier, CPCI 3U format

- 5 volts PCI signaling

- Support for up to two IP modules

- 8 MHz IP operation Per slot

- Direct I/O or Memory mapped access from CPCI bus via PCI Chip

- Supports double-wide form factor Industry Pack

- Full interrupt support of host

- Front panel I/O connectors for all IP’s

- Up to 100 I/O’s on one single slot

| Mechanical Interface | Switched Mezzanine Card (XMC) Interface confirming to ANSI/VITA 42.0-2008 (Auxiliary Standard) Standard single-width (149mm x 74mm) | |||||||||

| Electrical Interface | PCI Express x4 Link (Base Specification 2.1) compliant interface conforming to ANSI/VITA 42.3-2006 (PCI Express Protocol Layer Standard) | |||||||||

| PCI Express Switch | PI7C9X2G312GP (Pericom) | |||||||||

| PCI Express to PCI Bridge | XIO2001 (Texas Instruments) | |||||||||

| User configurable FPGA | TXMC639-10R: XC7K160T-2FBG676I (AMD) TXMC639-11R: XC7K325T-2FBG676I (AMD) | |||||||||

| SPI-Flash | MT25QL128 (Micron) 128 Mbit (contains TXMC639 FPGA BRD) or compatible; +3.3 V supply voltage | |||||||||

| DDR3 RAM | 2x MT41K256M16TW-107 (Micron) 256Meg x 32 bit | |||||||||

| Board Configuration Controller | LCMXO2-7000HC (Lattice) | |||||||||

| ADC | LTC2320 -16 (Analog Devices) | |||||||||

| DAC | AD5547BRUZ (Analog Devices) | |||||||||

| A/D Channels | TXMC639-10R: 8 Differential 16bit A/D Channels TXMC639-11R: 16 Differential 16bit A/D Channels Input Configuration per BCC Device: Input Voltage Ranges: Differental : ±20.57 V, ±10.28 V or ±5.14 V (Single-Ended: ±10.28 V, ±5.14 V or ±2.57 V) All analog inputs are connected via an impedance converter and a second operation amplifier for level adjustment and filtering to the differential ADC inputs. The -3 dB limit of this input stage is at approx. 8MHz | |||||||||

| D/A Channels | TXMC639-10R: 4 Single-Ended 16 Bit D/A Channels TXMC639-11R: 8 Single-Ended 16 Bit D/A Channels Output range configurable per D/A channel. Maximum single-ended Output Voltage – Vout: ±10 V Maximum Output Drive Current for each Output: 10 mA Maximum Capacitive Load for each Output: 1000 pF Typical Settling Time for a 10 mA / 1000 pF: < 1 µs | |||||||||

| Digital Front I/O Channels | 32 digital I/O Lines

| |||||||||

| Digital Rear I/O Channels | 64 direct FPGA I/O lines to P14 Rear I/O connector

4 MGT line to P16 Rear I/O connector

| |||||||||

| Front I/O | Front I/O Samtec – ERF8_050_01_L_D_RA_L_TR | |||||||||

| P14 Rear I/O | 64 pin Mezzanine Connector (Molex 71436-2864 or compatible) | |||||||||

| P16 Rear I/O | 114 pin Mezzanine Connector (Samtec – ASP-105885-01) | |||||||||

| Power Requirements 1) | Depends on FPGA design With TXMC639 Board Reference Design / without external load

| |||||||||

| Temperature Range | Operating: – 40 °C to + 85 °C Storage: – 55 °C to + 125 °C | |||||||||

| MTBF 1) | 157 000 h to 161 000 h | |||||||||

| Humidity | 5% – 95% non-condensing | |||||||||

| Weight | 140 g |

1) depends on variant, for further details see User Manual

TXMC639-10R

| 8x Analog In, 4x Analog Out, XC7K160T-2FBG676 Kintex™ 7 FPGA AMD Kintex™ 7 FPGA (XC7K160T-2FBG676), 1GB DDR3, 8x Analog In, 4x Analog Out, 32x digital Front I/O, 64x direct FPGA Rear I/O Lines and 4x MGTs Rear I/O |

TXMC639-11R

| 16x Analog In, 8x Analog Out, XC7K325T-2FBG676 Kintex™ 7 FPGA AMD Kintex™ 7 FPGA (XC7K325T-2FBG676), 1GB DDR3, 16x Analog In, 8x Analog Out, 32x digital Front I/O, 64x direct FPGA Rear I/O Lines and 4x MGTs Rear I/O |